.

### **CONTENTS**

| INTRODUCING THE SERIES 3000 BIPOLAR MICROPROCESSOR          | 3  |

|-------------------------------------------------------------|----|

| N3001 MICROPROGRAM CONTROL UNIT                             | 9  |

| N3002 CENTRAL PROCESSING ELEMENT                            | 20 |

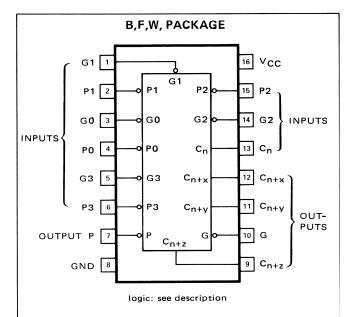

| S54/N74S182 HIGH SPEED LOOK-AHEAD CARRY GENERATOR 3         | 32 |

| <b>82S09</b> 576-BIT BIPOLAR RAM (64x9)                     | 35 |

| <b>82S10</b> 1024x1 BIT BIPOLAR RAM (OPEN COLLECTOR) 3      | 39 |

| <b>82S11</b> 1024x1 BIT BIPOLAR RAM (TRI-STATE)             | 39 |

| <b>82S25</b> 64-BIT BIPOLAR SCRATCH PAD MEMORY (16x4 RAM) 4 |    |

| <b>82S100</b> BIPOLAR FIELD-PROGRAMMABLE LOGIC ARRAY 4      | 17 |

| (16x8x48 FPLA)—TRI-STATE                                    |    |

| <b>82S101</b> BIPOLAR FIELD-PROGRAMMABLE LOGIC ARRAY 4      | 17 |

| (16x8x48 FPLA)—OPEN COLLECTOR                               |    |

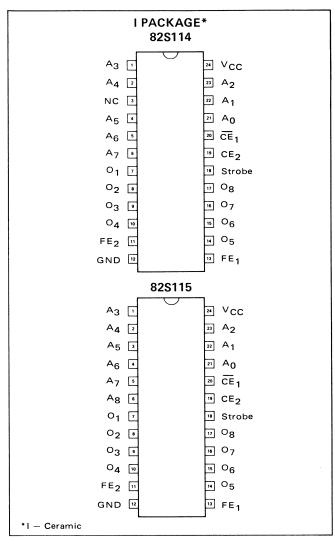

| <b>82S114</b> 2048-BIT BIPOLAR ROM (256x8 PROM) 5           | 52 |

| <b>82S115</b> 4096-BIT BIPOLAR ROM (512x8 PROM) 5           | 52 |

|                                                             | 58 |

|                                                             | 58 |

| •                                                           | 32 |

| · · · · · · · · · · · · · · · · · · ·                       | 32 |

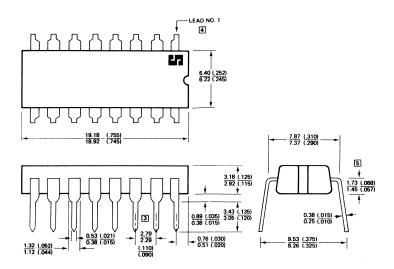

| <b>8T26A</b> TRI-STATE QUAD BUS TRANSCEIVER 6               |    |

| <b>8T28</b> TRI-STATE QUAD BUS TRANSCEIVER 6                |    |

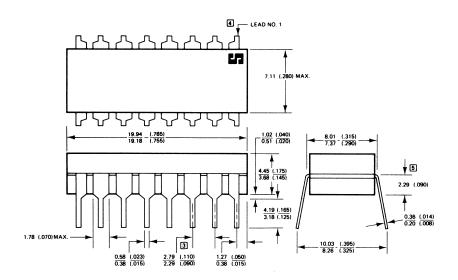

| <b>8T31</b> 8-BIT BIDIRECTIONAL I/O PORT                    | 11 |

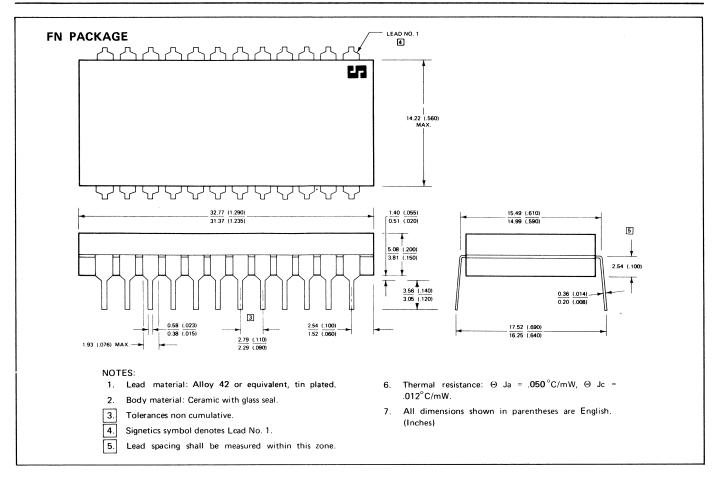

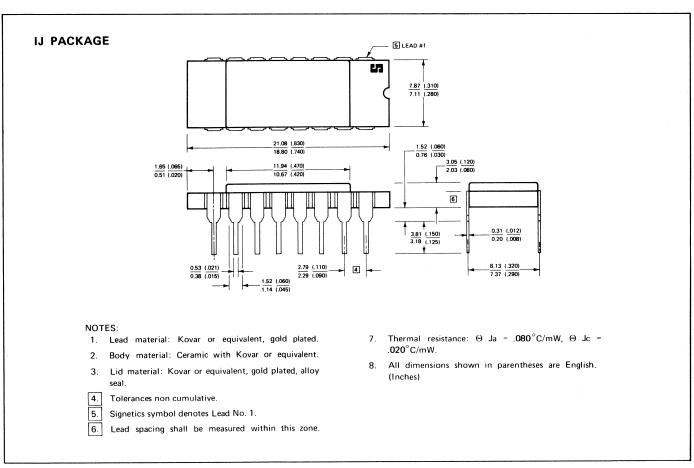

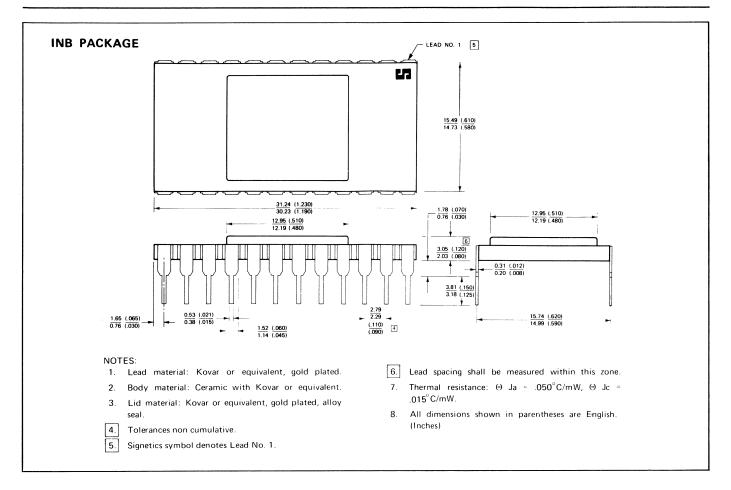

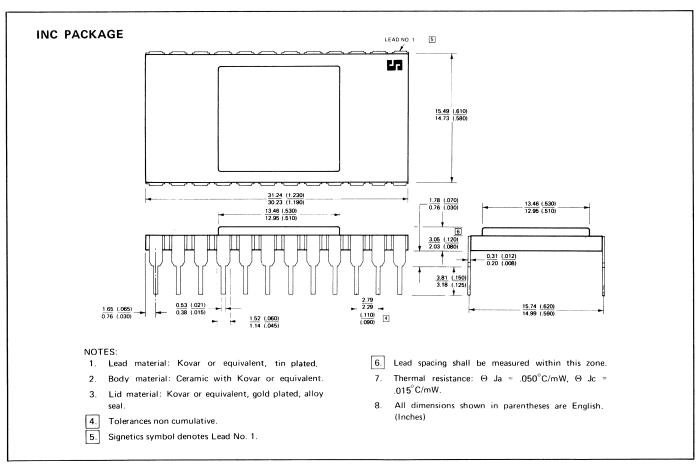

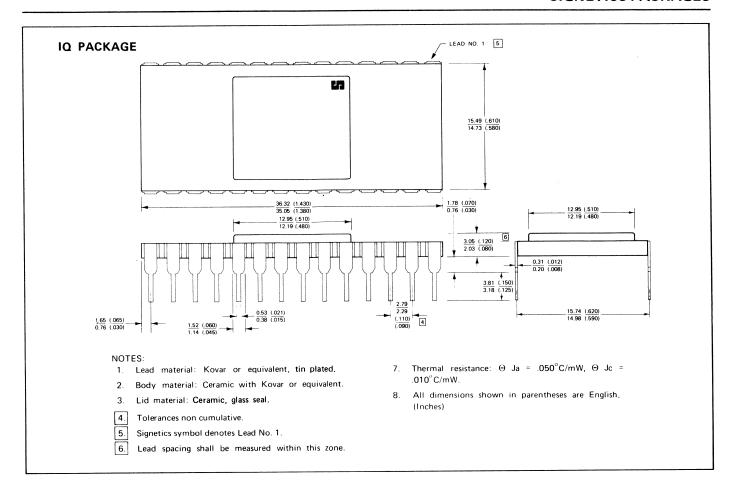

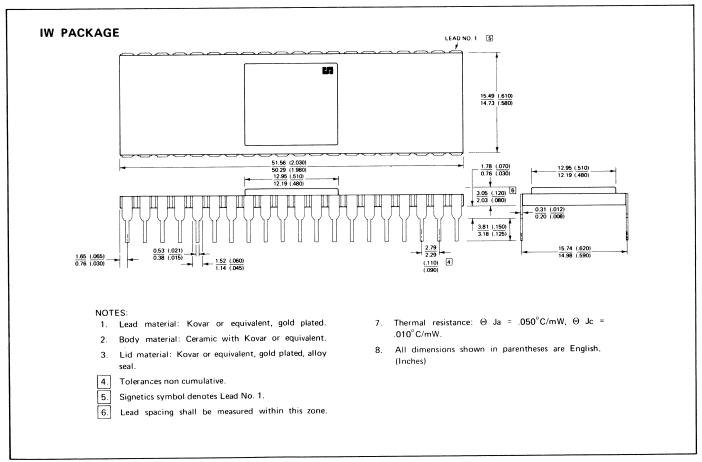

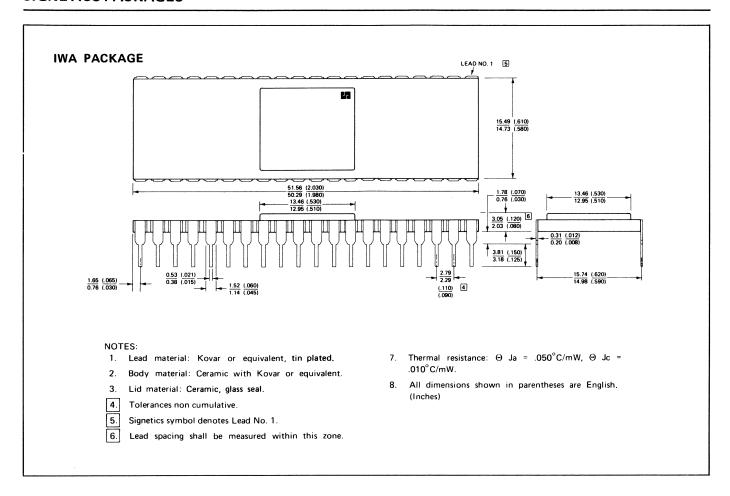

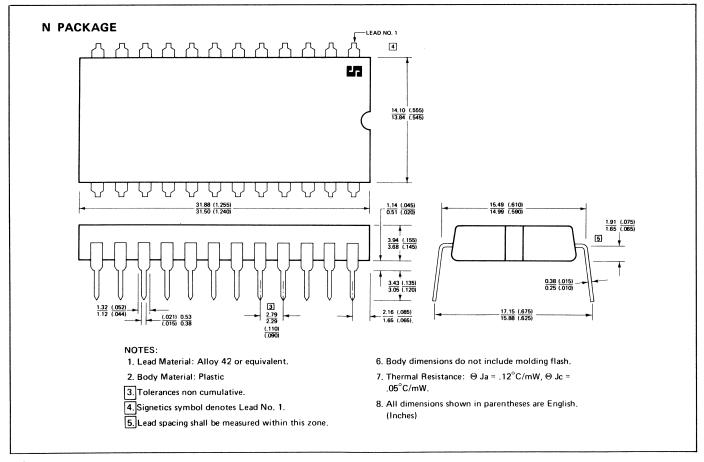

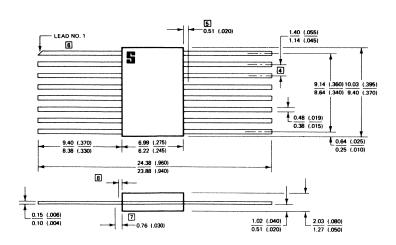

| PACKAGE INFORMATION 7                                       | 74 |

# INTRODUCING THE SERIES 3000 BIPOLAR MICROPROCESSOR

The introduction of the Signetics Series 3000 Bipolar Microprocessor Chip Set has brought new levels of high performance to microprocessor applications not previously possible with MOS technology. Combining the Schottky bipolar N3001 Microprogram Control Unit (MCU) and N3002 Central Processing Element (CPE) with industry standard memory and support circuits, microinstruction cycle times of 100 nanoseconds are possible.

In the majority of cases, the choice of a bipolar microprocessor slice, as opposed to an MOS device, is based on speed or flexibility of microprogramming. Starting with these characteristics, the design of the Signetics Series 3000 Microprocessor has been optimized around the following objectives:

- Fast cycle time

- All memory and support chips are industry standard

- Cooler operation

- Lower total system cost

Futhermore, systems built with large-scale integrated circuits are much smaller and require less power than equivalent systems using medium and/or small scale integrated circuits.

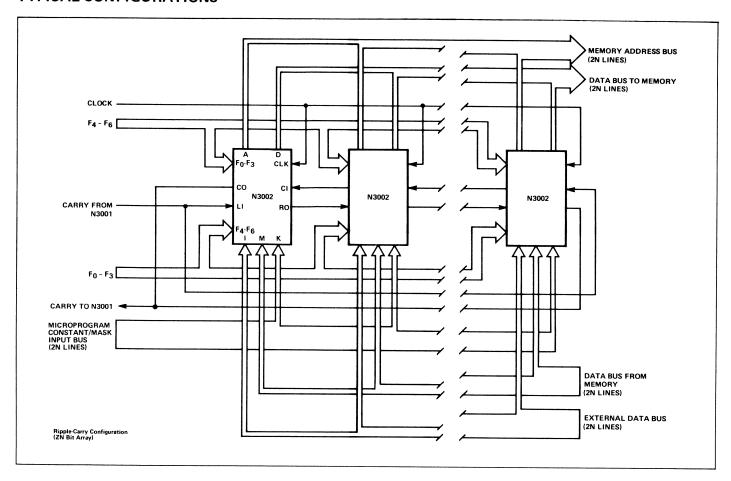

The two components of the Series 3000 chip set, when combined with industry standard memory and peripheral circuits, allows the design engineer to construct high-performance processors and/or controllers with a minimum amount of auxillary logic. Features such as the multiple independent address and data buses, tri-state logic, and separate output enable lines eliminate the need for time-multiplexing of buses and associated hardware.

Each Central Processing Element represents a

complete 2-bit slice through the data processing section of a computer. Several CPE's may be connected in parallel to form a processor of any desired word length. The Microprogram Control Unit controls the sequence in which microinstructions are fetched from the microprogram memory (ROM/PROM), with these microinstructions controlling the step-by-step operation of the processor.

Each CPE contains a 2-bit slice of five independent buses. Although they can be used in a variety of ways, typical connections are:

Input M-bus: Carries data from external

memory

Input I-bus: Carries data from input/

output device

Input K-bus: Used for microprogram mask

or literal (constant) value

input

Output A-bus: Connected to CPE Memory

Address Register

Output D-bus: Connected to CPE accumula-

or.

As the CPE's are paralleled together, all buses, data paths, and registers are correspondingly expanded.

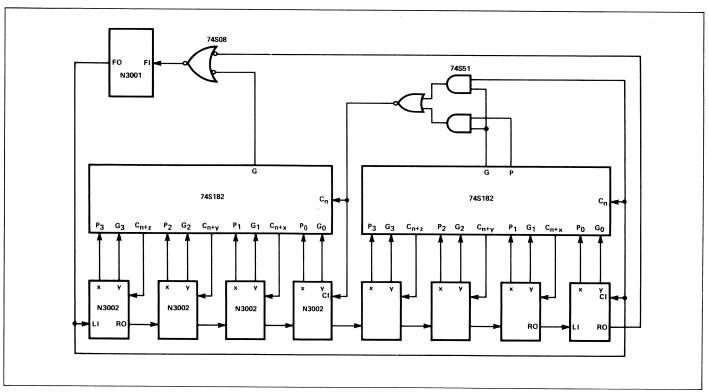

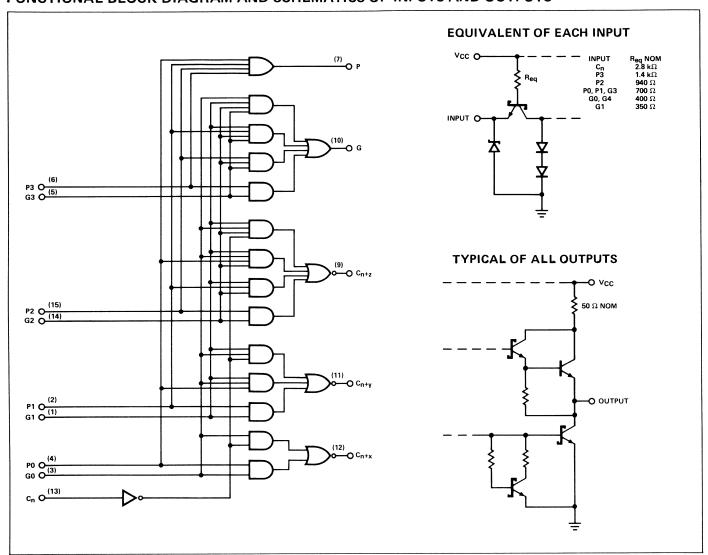

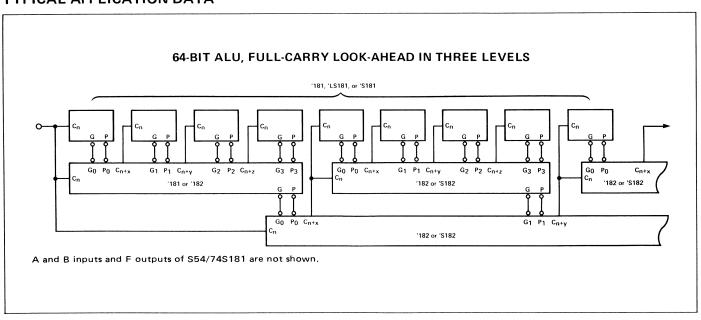

The microfunction input bus (F-bus) controls the internal operation of the CPE, selecting both the operands and the operation to be executed upon them. The arithmetic logic unit (ALU), controlled by the microfunction decoder, is capable of over 40 Boolean and binary operations as outlined in the FUNCTION DESCRIPTION section of the N3002 data sheet. Standard carry look-ahead outputs (X and Y) are generated by the CPE for use with industry standard devices such as the 74S182.

# FEATURES OF THE SERIES 3000 MICROCESSOR CHIP SET

#### N3001

- Signetics Schottky TTL process

- 45 ns cycle time (typ.)

- Direct addressing of standard bipolar PROM or ROM

- 512 microinstruction addressability

- 4 bit program latch

- 3 flag registers

- 11 address control (jump) functions

- 8 flag control functions

#### N3002

- 45 ns cycle time (typ.)

- Easy expansion to 2N bits word length

- 11 general purpose registers

- Full function accumulator

- 2's complement arithmetic

- Logical AND, OR, NOT, Exclusive NOR

- Increment, decrement, shift left/right

- Bit testing and zero detect

- Carry look-ahead generation

- Masking via K-bus

- Nondestructive testing of data in accumulator and scratchpad

- 3 input buses

- 2 output buses

# FEATURES OF COMPATIBLE PRODUCTS

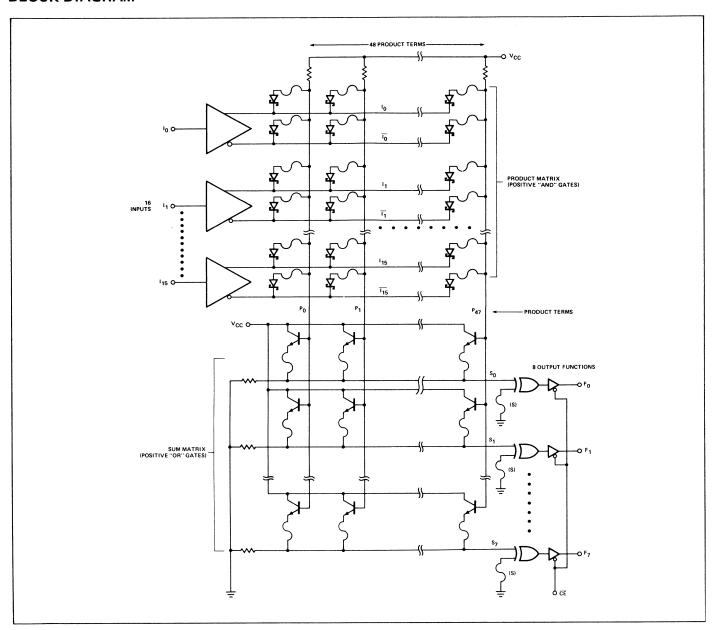

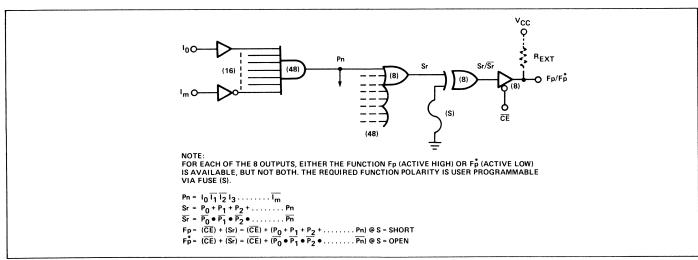

#### 82S100, 82S101 FPLA

- Field programmable (Ni-Cr Link)

- Input variables 16

- Output functions 8

- Product terms 48

- Address access time 50 ns

- Tri-state (82S100) or open collector (82S101) outputs

- 28 pin ceramic dip

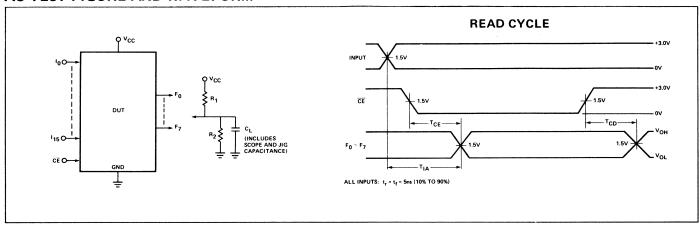

#### 82S115/123/129 PROMs

- Schottky TTL technology

- Single +5V power supply

- 32 x 8 organization (82S123)

- 256 x 8 organization (82S129)

- 512 x 8 organization (82S115)

- Field programmable (Nichrome)

- On-chip storage latches (82S115 only)

- Low current pnp inputs

- Tri-state outputs

- 35 ns typical access time

- Standard 24 pin DIP (82S115)

- Standard 16 pin DIP (82S123, 82S129)

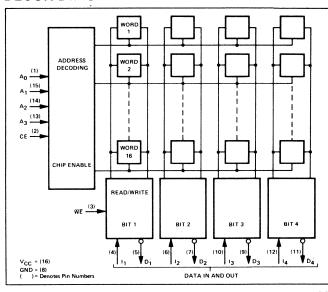

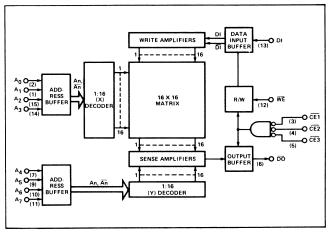

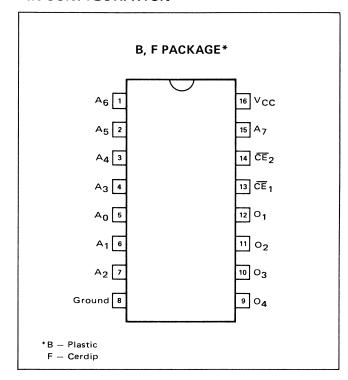

#### 82S25/82S116/82S11 RAMs

- Schottky TTL technology

- 16 x 4 organization (82S25)

- 256 x 1 organization (82S116)

- 1024 x 1 organization (82S11)

- On-chip address decoding

- 16 pin ceramic dip

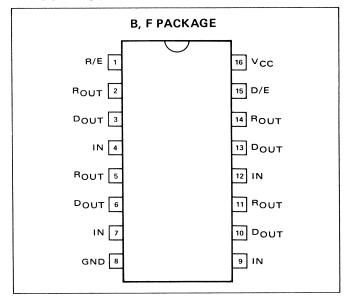

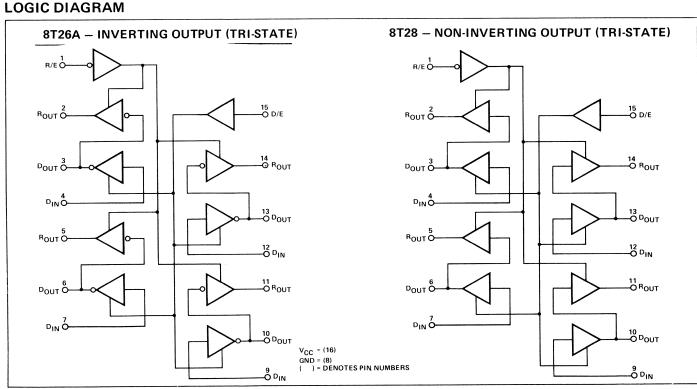

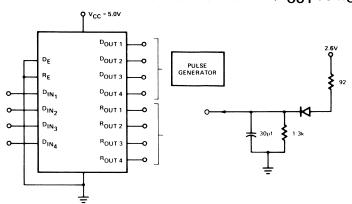

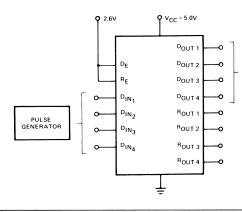

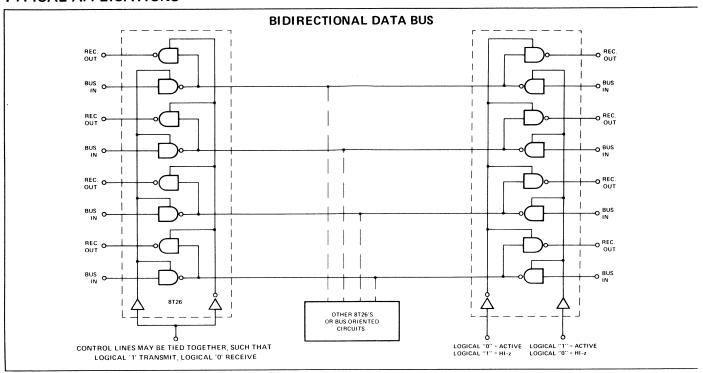

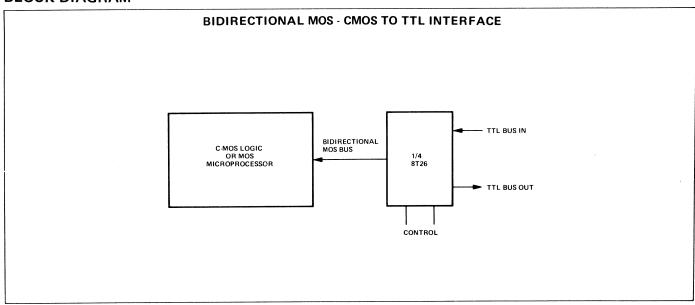

#### 8T26A/8T28 Quad Transceiver

- Schottky TTL technology

- Four pairs of bus drivers/receivers

- Separate drive and receive enable lines

- Tri-state outputs

- Low current pnp inputs

- High fan out driver sinks 40mA

- 20 ns maximum propagation delay

- Standard 16 pin DIP

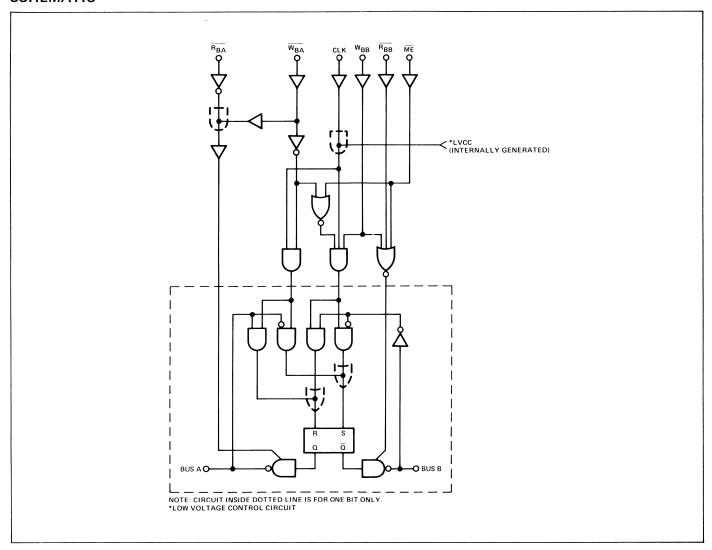

#### 8T31 8-bit Bidirectional Port

- Schottky TTL technology

- Two independent bidirectional busses

- Eight bit latch register

- Independent read, write controls for each bus

- Bus A overrides if a write conflict occurs

- Register can be addressed as a memory location

- via Bus B Master Enable

- 30 ns maximum propagation delay

- Low input current: 500μ A

- High fan out sinks 20mA

- Standard 24 pin DIP

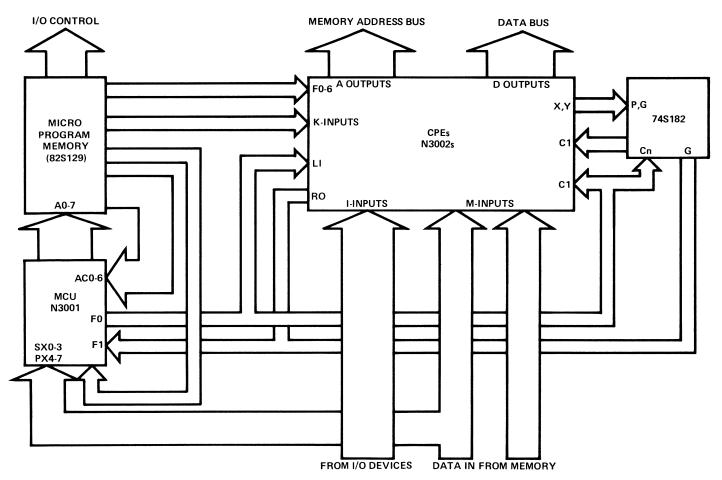

A typical processor configuration is shown in Figure 1. It should be remembered that in working with slice-oriented microprocessors, the final configuration may be varied to enhance speed, reduce component count, or increase data-processing capability. One method of maximizing

a processor's performance is called pipelining. To accomplish this, a group of D-type flip-flops or latches (such as the 74174 Hex D-type Flip-Flop) are connected to the microprogram memory outputs (excluding the address control field  $AC_0$  –  $AC_6$ ) to buffer the current microinstruction

Figure 1: MICROCOMPUTER BLOCK DIAGRAM

and allow the MCU to overlap the fetch of the next instruction with the execution of the current one. The time saved in pipelining operations is the shorter of either the address set-up time to the microprogram memory (ROM/PROM) or the access time of the ROM/PROM. A convenient way of implementing pipelining is to use ROMs with on-board latches, such as the Signetics 82S115.

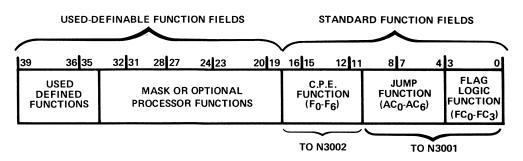

Figure 2 shows a typical microinstruction format using the 82S129 PROMs contained in the Signetics 3000 Microprocessor Designer's Evaluation Kit. Although this particular example is for a 40-bit word (10 PROMs), the allocation of bits for the mask (K-bus) and optional processor functions depands on the specific application of the system and the trade offs which the designer wishes to make.

In using the K-bus, it should be kept in mind that the K inputs are always ANDed with the B-multiplexer outputs into the ALU. Bit masking, frequently done in computer control systems, can be performed with the mask supplied to the K-bus directly from the microinstruction.

By placing the K-bus in either the all-one or all-zero condition (done with a single control bit in the microinstruction), the accumulator will either be selected or de-selected, respectively, in a given operation. This feature nearly doubles the amount of microfunctions in the CPE. A description of these various microfunctions can be found in the N3002 data sheet under the heading "FUNCTION DESCRIPTION" by referring to the K-bus conditions of all-ones (11) and all-zeros (00).

The MCU controls the sequence in which microinstructions are fetched from the microprogram memory (ROM/PROM). In its classical form, the MCU would use a next-address field in each microinstruction. However, the N3001 uses a modified classical approach in which the microinstruction field specifies conditional tests on the MCU bus inputs and registers. The next-address logic of the MCU also makes extensive use of a row/column addressing scheme, whereby the next address is defined by a 5-bit row address and 4-bit column address. Thus, from a particular address location, it is possible to jump unconditionally to any other location within that row or

Figure 2: TYPICAL MICROINSTRUCTION FORMAT.

Note: The mask field need only be used during masking operations. At other times, it is entirely user definable

column, or conditionally to other specified locations in one operation. Using this method, the processor functions can be executed in aprallel with program branches.

As an example of this flexibility, let us assume a disk controller is being designed. As part of the sequence logic, three bits of the disk drive status word must be tested and all three must be true in order to proceed with the particular sequencing operation. In any sequencing operation using a status word for conditional branch information, there are innumerable combinations of bits which must be tested throughout the sequencing operation. Using discrete logic techniques, this would involve several levels of gating.

However, the entire operation can be done in two microinstructions. First, the mask (K-bus) field in the microinstruction format is encoded with a one for each corresponding status bit to be tested and a zero for each bit to be discarded. The status word is input via the I-bus and ANDed with the K-bus mask using the CPE microfunction operation from F-Group 2, R-Group III. Assuming we are using low-true logic (TRUE = 0 Volts), we now test the result, which is located in the accumulator AC, for all zeros using the CPE microfunction operation from F-Group 5, R-Group III. Depending on the zero/non-zero status of AC, a one or zero will be loaded into the carryout CO bit. This

bit can now be used as a condition for the next address jump calculation within the N3001 MCU. If the AC was zero (status word was true), we will jump to the next address within our controller sequence. If the AC was non-zero (status word not true), then a jump would be made back to the beginning of this two-microinstruction loop and the test sequence repeated until the status word (all three bits) is true.

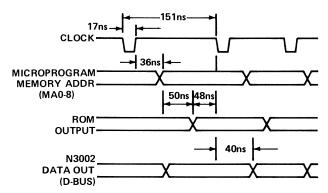

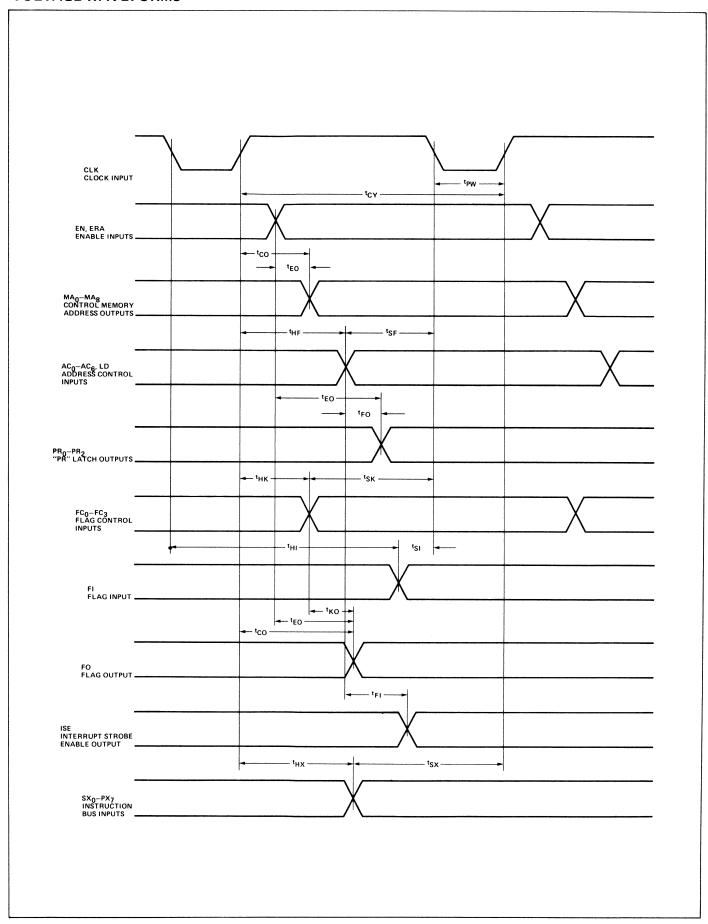

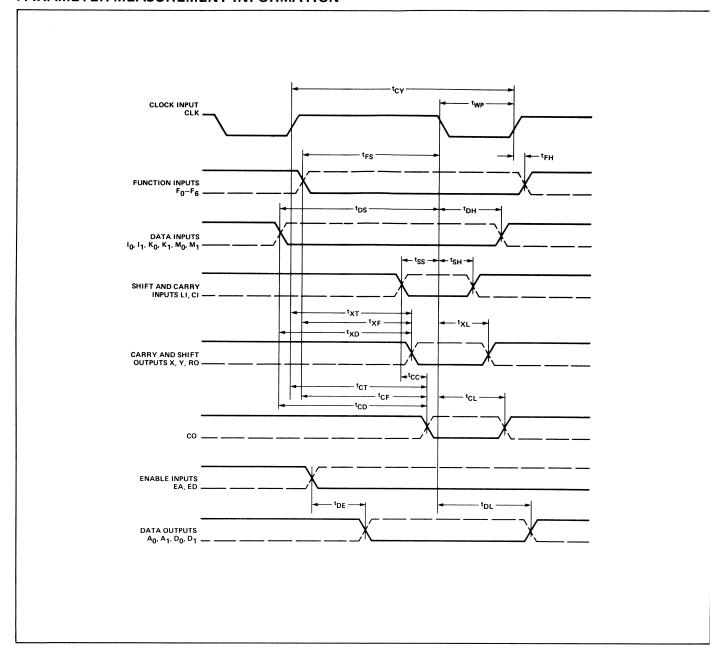

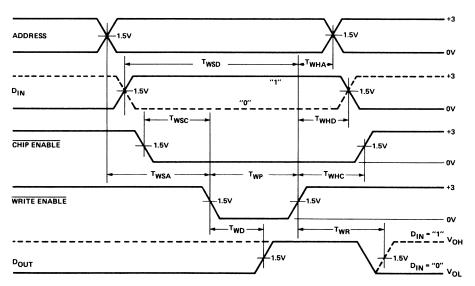

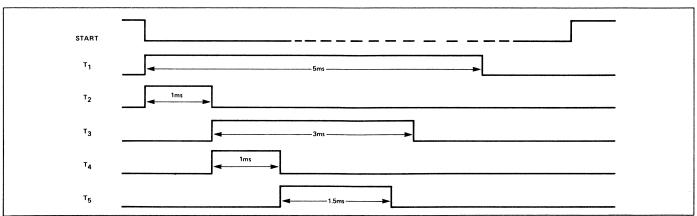

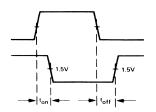

Figure 3 shows a typical timing diagram for a system operating in the non-pipelined mode. Keep in mind that the maximum clock rate is dependent upon the total of propagation delay times plus required set-up times. It is at the designer's discretion to resolve the speed versus complexity tradeoffs.

Figure 3: SYSTEM TIMING - NON-PIPELINED CONFIGURATION

# Sinnetics

#### PRELIMINARY INFORMATION

### BIPOLAR MICROPROCESSOR

#### **DESCRIPTION**

The N3001 MCU is one element of a bipolar microcomputer set. When used with the 3002, 74S182, ROM or PROM memory, a powerful microprogrammed computer can be implemented,

The 3001 MCU controls the fetch sequence of microinstructions from the microprogram memory. Functions performed by the 3001 include:

- Maintenance of microprogram address register

- Selection of next microinstruction address

- Decoding and testing of data supplied via several input busses

- Saving and testing of carry output data from the central processing (CP) array

- Control of carry/shift input data to the CP array

- Control of microprogram interrupts

#### **FEATURES**

- SCHOTTKY TTL PROCESS

- 45ns CYCLE TIME (TYP.)

- DIRECT ADDRESSING OF STANDARD BIPOLAR **PROM OR ROM**

- 512 MICROINSTRUCTION ADDRESSIBILITY

- ADVANCED ORGANIZATION:

- 9-BIT MICROPROGRAM ADDRESS REGISTER AND BUS ORGANIZED TO ADDRESS MEMORY BY ROW AND COLUMN

- 4-BIT PROGRAM LATCH

- 2 FLAG REGISTERS

- 11 ADDRESS CONTROL FUNCTIONS:

- 3 JUMP AND TEST LATCH FUNCTION

- 16 WAY JUMP AND TEST INSTRUCTION

- FLIGHT FLAG CONTROL FUNCTIONS:

- 4 FLAG INPUT FUNCTIONS

- 4 FLAG OUTPUT FUNCTIONS

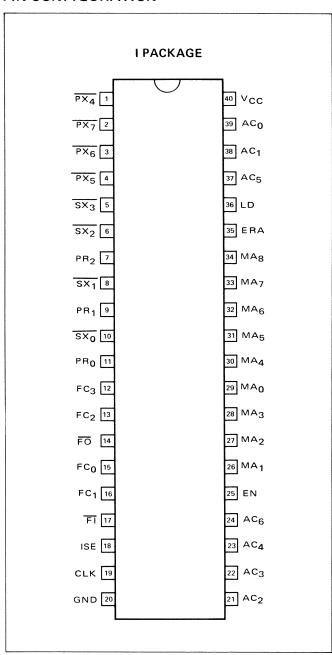

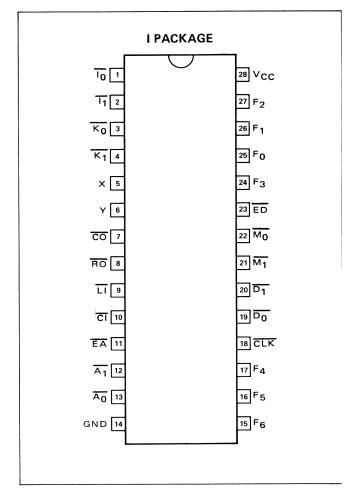

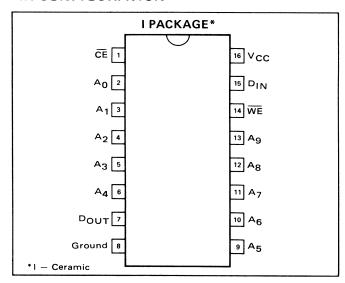

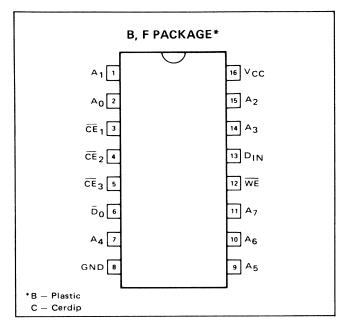

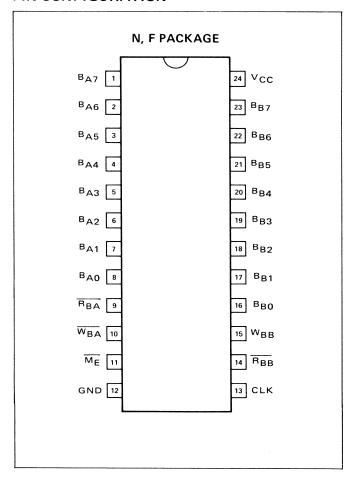

#### PIN CONFIGURATION

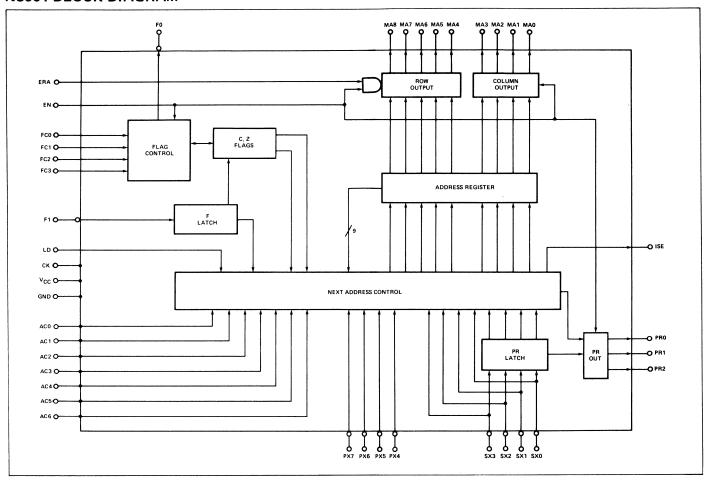

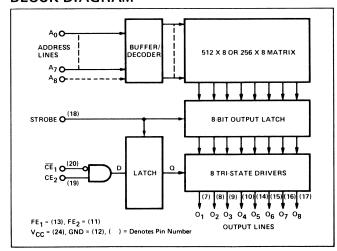

#### **N3001 BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| PIN               | SYMBOL                              | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                         | TYPE                      |

|-------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1-4               | PX <sub>4</sub> -PX <sub>7</sub>    | Primary Instruction Bus Inputs  Data on the primary instruction bus is tested by the JPX function to determine the next microprogram address.                                                                                                                                                                             | Active LOW                |

| 5, 6, 8, 10       | $\overline{SX_0} - \overline{SX_3}$ | Secondary Instruction Bus Inputs  Data on the secondary instruction bus is synchronously loaded into the PR-latch while the date on the PX-bus is being tested (JPX). During a subsequent cycle, the contents of the PR-latch may be tested by the JPR, JLL, or JRL functions to determine the next microprogram address. | Active LOW                |

| 7, 9, 11          | PR <sub>0</sub> -PR <sub>2</sub>    | PR-Latch Outputs The PR-latch outputs are asynchronously enabled by the JCE function. They can be used to modify microinstructions at the outputs of the microprogram memory or to provide additional control lines.                                                                                                      | Open Collector            |

| 12, 13,<br>15, 16 | FC <sub>0</sub> -FC <sub>3</sub>    | Flag Logic Control Inputs  The flag logic control inputs are used to cross-switch the flags (C and Z) with the flag logic input (FI) and the flag logic output (FO).                                                                                                                                                      | Active HIGH               |

| 14                | FO                                  | Flag Logic Output The outputs of the flags (C and Z) are multiplexed internally to form the common flag logic output. The output may also be forced to a logical O or logical 1.                                                                                                                                          | Active LOW<br>Three-state |

| 17                | FI                                  | Flag Logic Input The flag logic input is demultiplexed internally and applied to the inputs of the flags (C and Z). Note: The flag input data is saved in the F-latch when the clock input (CLK) is low.                                                                                                                  | Active LOW                |

#### PIN DESCRIPTION (Cont'd)

| PIN            | SYMBOL                           | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                    | TYPE        |

|----------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 18             | ISE                              | Interrupt Strobe Enable Output The interrupt strobe enable output goes to logical 1 when one of the JZR functions are selected (see Functional Description). It can be used to provide the strobe signal required by interrupt circuits.                                                                                             | Active HIGH |

| 19             | CLK                              | Clock Input                                                                                                                                                                                                                                                                                                                          |             |

| 20             | GND                              | Ground                                                                                                                                                                                                                                                                                                                               |             |

| 21-24<br>37-39 | AC <sub>0</sub> -AC <sub>6</sub> | Next Address Control Function Inputs All jump functions are selected by these control lines.                                                                                                                                                                                                                                         | Active HIGH |

| 25             | EN                               | Enable Input When in the HIGH state, the enable input enables the microprogram address, PR-latch and flag outputs.                                                                                                                                                                                                                   |             |

| 26-29          | $MA_0-MA_3$                      | Microprogram Column Address Outputs                                                                                                                                                                                                                                                                                                  | Three-state |

| 30-34          | $MA_4-MA_8$                      | Microprogram Row Address Outputs                                                                                                                                                                                                                                                                                                     | Three-state |

| 35             | ERA                              | Enable Row Address Input When in the LOW state, the enable row address input independently disables the microprogram row address outputs. It can be used to facilite the implementation of priority interrupt systems.                                                                                                               | Active HIGH |

| 36             | LD                               | Microprogram Address Load Input When the active HIGH state, the microprogram address load input inhibits all jump functions and synchronously loads the date on the instructions busses into the microprogram register. However, it does not inhibit the operation of the PR-latch or the generation of the interrupt strobe enable. | Active HIGH |

| 40             | Vcc                              | +5 Volt Supply                                                                                                                                                                                                                                                                                                                       |             |

#### THEORY OF OPERATION

The MCU controls the sequence of microinstructions in the microprogram memory. The MCU simultaneously controls 2 flip-flops (C, Z) which are interactive with the carry-in and carry-out logic of an array of CPEs.

The functional control of the MCU provides both unconditional jumps to new memory locations and jumps which are dependent on the state of MCU flags or the state of the "PR" latch. Each instruction has a "jump set" associated with it. This "jump set" is the total group of memory locations which can be addressed by that instruction.

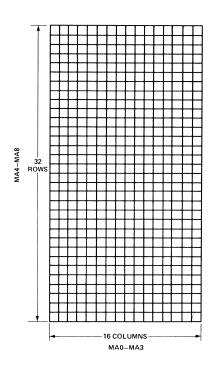

The MCU utilizes a two-dimensional addressing scheme in the microprogram memory. Microprogram memory is organized as 32 rows and 16 columns for a total of 512 words. Word length is variable according to application. Address is accomplished by a 9-bit address organized as row and column address.

#### SIGNETICS MICROPROGRAM CONTROL UNIT ■ N3001

#### **ABSOLUTE MAXIMUM RATINGS**

$0^{\circ}$ C to  $70^{\circ}$ C Operating Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C Storage Temperature 7V Supply Voltages +5.5V All Input Voltages 100mA Output Currents

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

#### DC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C$

|                      |                                                                                                                                                | 00NDITION                                                      |     | LIMITS                    |                         | UNIT           |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----|---------------------------|-------------------------|----------------|--|

|                      | (All Input Pins)  Input Load Current: CLK Input EN Input All Other Inputs Input Leakage Current: CLK EN Input                                  | TEST CONDITIONS                                                | MIN | TYP <sup>1</sup>          | MAX                     | ONT            |  |

| V <sub>C</sub>       | · · · · · ·                                                                                                                                    | V <sub>CC</sub> = 4.75, I <sub>C</sub> = -5mA                  |     | -0.8                      | -1.0                    | <b>V</b>       |  |

| 1 <sub>F</sub>       | CLK Input<br>EN Input                                                                                                                          | $V_{CC} = 5.25V, V_F = 0.45V$                                  |     | -0.075<br>-0.05<br>-0.025 | -0.75<br>-0.50<br>-0.25 | mA<br>mA<br>mA |  |

| 1 <sub>R</sub>       | CLK                                                                                                                                            | V <sub>CC</sub> = 5.25V, V <sub>R</sub> = 5.25V                |     |                           | 120<br>80<br>40         | μΑ<br>μΑ<br>μΑ |  |

| VIL                  | Input Low Voltage                                                                                                                              | V <sub>CC</sub> = 5.0V                                         |     |                           | 0.8                     | V              |  |

| ۷ηн                  | Input High Voltage                                                                                                                             |                                                                | 2.0 |                           |                         | V              |  |

| СС                   | Power Supply Current                                                                                                                           | $V_{CC} = 5.25V^2$                                             |     | 170                       | 240                     | mA             |  |

| VoL                  | Output Low Voltage<br>(All Output Pins)                                                                                                        | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 10mA                |     | 0.35                      | 0.45                    | V              |  |

| V <sub>ОН</sub>      | Output High Voltage<br>(MA <sub>0</sub> -MA <sub>8</sub> , ISE, FO)                                                                            | V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = -1mA                | 2.4 | 3.0                       |                         | V              |  |

| l <sub>os</sub>      | Output Short Circuit Current (MA <sub>0</sub> -MA <sub>8</sub> , ISE, FO)                                                                      | V <sub>CC</sub> = 5.0V                                         | -15 | -28                       | -60                     | mA             |  |

| I <sub>o (off)</sub> | Off-State Output Current:<br>PR <sub>0</sub> -PR <sub>2</sub> , MA <sub>0</sub> -MA <sub>2</sub> , FO<br>MA <sub>0</sub> -MA <sub>8</sub> , FO | $V_{CC} = 5.25V, V_o = 0.45V$<br>$V_{CC} = 5.25V, V_o = 5.25V$ |     |                           | - 100<br>- 100          | μA<br>μA       |  |

Typical values are for T<sub>A</sub> = 25°C and 5.0 supply voltage.

EN input grounded, all other inputs and outputs open.

JCF

#### **FUNCTIONAL DESCRIPTION**

The following is a description of each of the eleven address control functions. The symbols shown below are used to specify row and column addresses.

| SYMBOL           | MEANING                                                          |

|------------------|------------------------------------------------------------------|

| row <sub>n</sub> | 5-bit next row address where n is the decimal row address.       |

| col <sub>n</sub> | 4-bit next column address where n is the decimal column address. |

# UNCONDITIONAL ADDRESS CONTROL (JUMP) FUNCTIONS

The jump functions use the current microprogram address (i.e., the contents of the microprogram address register prior to the rising edge of the clock) and several bits from the address control inputs to generate the next microprogram address.

| MNEMONIC | FUNCTION DESCRIPTION                                                                                                                                                                                                                                               |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

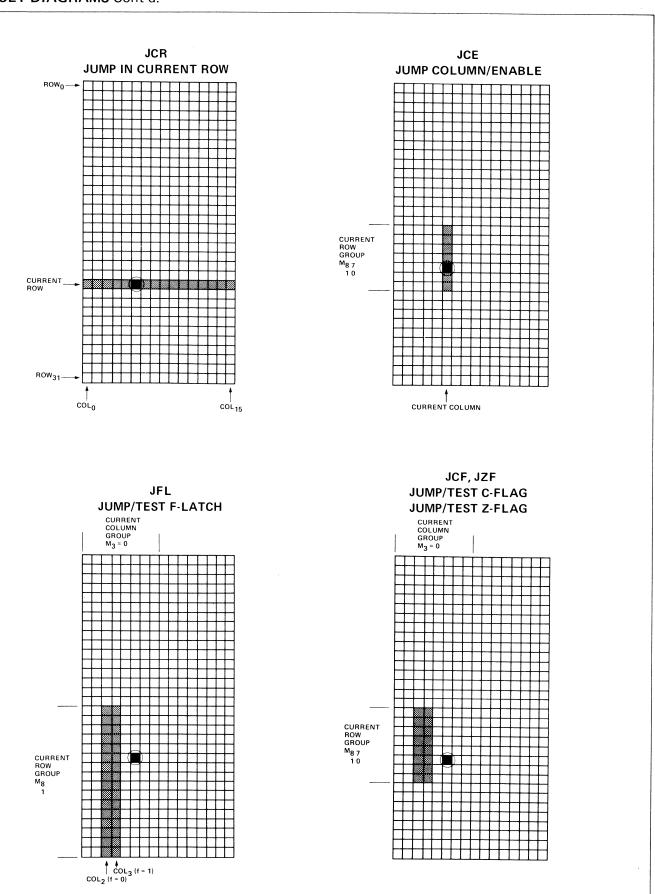

| JCC      | Jump in current column. $AC_0-AC_4$ are used to select 1 of 32 row addresses in the current column, specified by $MA_0-MA_3$ , as the next address.                                                                                                                |

| JZR      | Jump to zero row. $AC_0-AC_3$ are used to select 1 of 16 column addresses in $row_0$ , as the next address.                                                                                                                                                        |

| JCR      | Jump in current row. $AC_0-AC_3$ are used to select 1 of 16 addresses in the current row, specified by $MA_4-MA_8$ , as the next address.                                                                                                                          |

| JCE      | Jump in current column/row group and enable PR-latch outputs, $AC_0-AC_2$ are used to select 1 of 8 row addresses in the current row group, specified by $MA_7-MA_8$ , as the next row address. The current column is specified by $MA_0-MA_3$ . The PR-latch out- |

# FLAG CONDITIONAL ADDRESS CONTROL (JUMP/TEST) FUNCTIONS

The jump/test flag functions use the current microprogram address, the contents of the selected flag or latch, and several bits from the address control function to generate the next microprogram address.

puts are asynchronously enabled.

| MNEMONIC | FU        | NCTION   | DESCRIPTI   | ON  |

|----------|-----------|----------|-------------|-----|

| JFL      | Jump/test | F-latch. | $AC_0-AC_3$ | are |

Jump/test F-latch. AC<sub>0</sub>—AC<sub>3</sub> are used to select 1 of 16 row addresses in the current row group, specified by MA<sub>8</sub>, as the next row address. If the current column group, specified by MA<sub>3</sub>, is col<sub>0</sub>—col<sub>7</sub>, the F-latch is used to select col<sub>2</sub> or col<sub>3</sub> as the next column address. If MA<sub>3</sub> specifies column group col<sub>8</sub>—col<sub>15</sub>, the F-latch is used to select col<sub>10</sub> or col<sub>11</sub> as the next column address.

Jump/test C-flag. AC<sub>0</sub>—AC<sub>2</sub> are used to select 1 of 8 row addresses in the current row group, specified by MA<sub>7</sub> and MA<sub>8</sub>, as the next row address. If the current column group specified by MA<sub>8</sub> is col<sub>0</sub>—col<sub>7</sub>, the C-flag is used to select col<sub>2</sub> or col<sub>3</sub> as the next column address. If MA<sub>3</sub> specifies column group col<sub>8</sub>—col<sub>15</sub>, the C-flag is used to select col<sub>10</sub> or col<sub>11</sub> as the next column address.

JZF Jump/test Z-flag. Identical to the JCF function described above, except that the Z-flag, rather than the C-flag, is used to select the next column address.

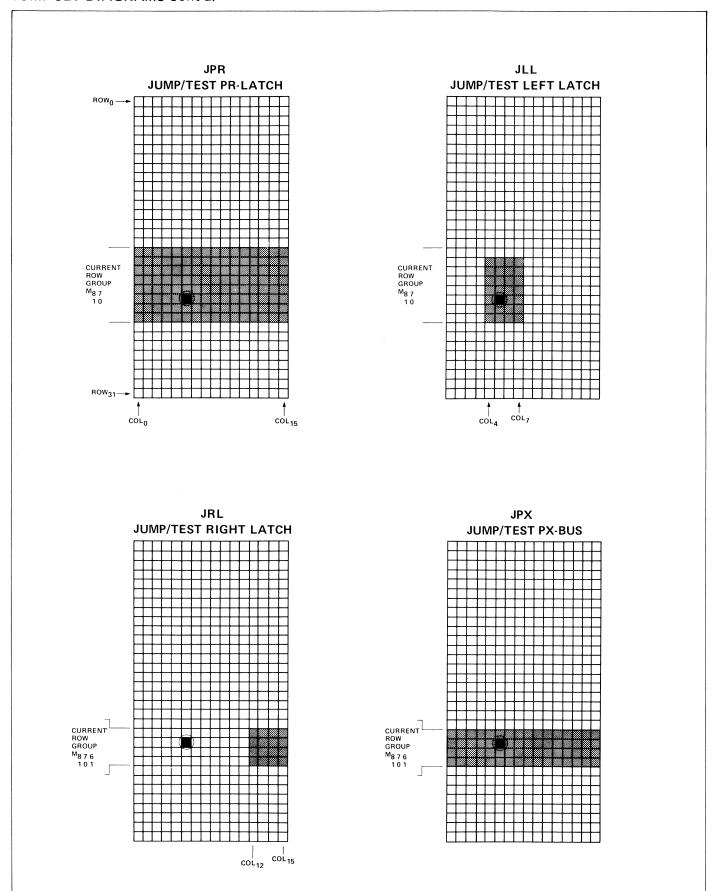

## PX-BUS AND PR-LATCH CONDITIONAL ADDRESS CONTROL (JUMP/TEST) FUNCTIONS

The PX-bus jump/test function uses the data on the primary instruction bus  $(PX_4-PX_7)$ , the current microprogram address, and several selection bits from the address control function to generate the next microprogram address. The PR-latch jump/test functions use the data held in the PR-latch, the current microprogram address, and several selection bits from the address control function to generate the next microprogram address.

| MNEMONIC | FUNCTION DESCRIPTION                                                                                                                                                                                                                                                                                                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JPR      | Jump/test PR-latch. $AC_0-AC_2$ are used to select 1 of 8 row addresses in the current row group, specified by MA <sub>7</sub> and MA <sub>8</sub> , as the next row address. The four PR-latch bits are used to select 1 of 16 possible column addresses as the next column address.                                          |

| JLL      | Jump/test leftmost PR-latch bits. $AC_0-AC_2$ are used to select 1 of 8 row addresses in the current row group, specified by $MA_7$ and $MA_8$ , as the next row address. $PR_2$ and $PR_3$ are used to column addresses in $col_4$ through $col_7$ as the next column address.                                                |

| JRL      | Jump/test rightmost PR-latch bits. $AC_0$ and $AC_1$ are used to select 1 of 4 high-order row addresses in the current row group, specified by $MA_7$ and $MA_8$ , as the next row address. $PR_0$ and $PR_1$ are used to select 1 of 4 possible column addresses in $col_{12}$ through $col_{15}$ as the next column address. |

| JPX      | Jump/test PX-bus and load PR-latch. $AC_0$ and $AC_1$ are used to select 1 of 4 row addresses in the current row group, specified by $MA_6$ – $MA_8$ , as the next row address. $PX_4$ – $PX_7$ are used to select 1 of 16 possible column addresses as the next column address. $SX_0$ – $SX_3$ data is locked in the         |

PR-latch at the rising edge of the clock.

# PX-BUS AND PR-LATCH CONDITIONAL ADDRESS CONTROL (JUMP/TEST) FUNCTIONS (Continued)

The flag control functions of the MCU are selected by the four input lines designated FC<sub>0</sub>-FC<sub>3</sub>. Function code formats are given in "Flag Control Function summary".

The following is a detailed description of each of the eight flag control functions.

#### FLAG INPUT CONTROL FUNCTIONS

The flag input control functions select which flag or flags will be set to the current value of the flag input (FI) line. Data on FI is stored in the F-latch when the clock is low. The content of the F-latch is loaded into the C and/or Z flag on the rising edge of the clock.

| MNEMONIC | FUNCTION DESCRIPTION                                                                    |

|----------|-----------------------------------------------------------------------------------------|

| SCZ      | Set C-flag and Z-flag to FI. The C-flag and the Z-flag are both set to the value of FI. |

| STZ      | Set Z-flag to FI. The Z-flag is set to the value of FI. The C-flag is unaffected.       |

| STC      | Set C-flag to FI. The C-flag is set to the value of FI. The Z-flag is unaffected.       |

| HCZ      | Hold C-flag and Z-flag. The values in the C-flag and Z-flag are unaffected.             |

#### FLAG OUTPUT CONTROL FUNCTIONS

The flag output control functions select the value to which the flag output (FO) line will be forced.

| MNEMONIC | <b>FUNCTION DESCRIPTION</b>                             |

|----------|---------------------------------------------------------|

| FFO      | Force FO to O. FO is forced to the value of logical O.  |

| FFC      | Force FO to C. FO is forced to the value of the C-flag. |

| FFZ      | Force FO to Z. FO is forced to the value of the Z-flag. |

| FF1      | Force FO to 1. FO is forced to the value of logical 1.  |

#### STROBE FUNCTIONS

The load function of the MCU is controlled by the input line designated LD. If the LD line is active HIGH at the rising edge of the clock, the date on the primary and secondary instruction busses,  $PX_4-PX_7$  and  $SX_0-SX_3$ , is loaded into the microprogram address register.  $PX_4-PX_7$  are loaded into  $MA_0-MA_3$  and  $SX_0-SX_3$  are loaded into  $MA_4-MA_7$ . The high-order bit of the microprogram address register  $MA_8$  is set to a logical 0. The bits from the primary instruction bus select 1 of 16 possible column addresses. Likewise, the bits from the secondary instruction bus select 1 of the first 16 row addresses.

The MCU generates an interrupt strobe enable on the output line designated ISE. The line is placed in the active high state whenever a JZR to  $\mathrm{col}_{15}$  is selected as the address control function. Generally, the start of a macroinstruction fetch sequence is situated at  $\mathrm{row}_0$  and  $\mathrm{col}_{15}$  so the interrupt control may be enabled at the beginning of

#### ADDRESS CONTROL FUNCTION SUMMARY

| ****     | DECORUPTION             | FUNCTION |   |            |                |                |                | <b>NEXT ROW</b> |                 |                |                |                | NEXT COL       |                 |                |                  |                |

|----------|-------------------------|----------|---|------------|----------------|----------------|----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|----------------|------------------|----------------|

| MNEMONIC | DESCRIPTION             | ACe      | 5 | 4          | 3              | 2              | 1              | 0               | MA <sub>8</sub> | 7              | 6              | 5              | 4              | MA <sub>3</sub> | 2              | 1                | 0              |

| JCC      | Jump in current column  | 0        | 0 | d <b>4</b> | d <sub>3</sub> | d <sub>2</sub> | d <sub>1</sub> | d <sub>0</sub>  | d <b>4</b>      | d <sub>3</sub> | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | m <sub>3</sub>  | $m_2$          | · m <sub>1</sub> | m <sub>0</sub> |

| JZR      | Jump to zero row        | 0        | 1 | 0          | d <sub>3</sub> | d <sub>2</sub> | d <sub>1</sub> | d <sub>0</sub>  | 0               | 0              | 0              | 0              | 0              | d <sub>3</sub>  | $d_2$          | d <sub>1</sub>   | d <sub>0</sub> |

| JCR      | Jump in current row     | 0        | 1 | 1          | $d_3$          | $d_2$          | d <sub>1</sub> | d <sub>0</sub>  | mg              | m <sub>7</sub> | m <sub>6</sub> | m <sub>5</sub> | m4             | d <sub>3</sub>  | $d_2$          | d <sub>1</sub>   | d <sub>0</sub> |

| JCE      | Jump in column/enable   | 1        | 1 | 1          | 0              | $d_2$          | d <sub>1</sub> | $d_{0}$         | mg              | m <sub>7</sub> | $d_2$          | d <sub>1</sub> | $d_0$          | m <sub>3</sub>  | $m_2$          | m <sub>1</sub>   | m <sub>0</sub> |

| JFL      | Jump/test F-latch       | 1        | 0 | 0          | d <sub>3</sub> | $d_2$          | d <sub>1</sub> | d <sub>0</sub>  | mg              | d <sub>3</sub> | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | m <sub>3</sub>  | 0              | 1                | f              |

| JCF      | Jump/test C-flag        | 1        | 0 | 1          | 0              | $d_2$          | $d_1$          | $d_0$           | mg              | m <sub>7</sub> | $d_2$          | $d_1$          | $d_{0}$        | m <sub>3</sub>  | 0              | 1                | С              |

| JZF      | Jump/test Z-flag        | 1        | 0 | 1          | 1              | $d_2$          | d <sub>1</sub> | $d_0$           | mg              | m <sub>7</sub> | $d_2$          | $d_1$          | d <sub>0</sub> | m <sub>3</sub>  | 0              | 1                | z              |

| JPR      | Jump/test PR-latch      | 1        | 1 | 0          | 0              | d <sub>2</sub> | d <sub>1</sub> | d <sub>0</sub>  | mg              | m <sub>7</sub> | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | р3              | p <sub>2</sub> | p <sub>1</sub>   | p <sub>0</sub> |

| JLL      | Jump/test left PR bits  | 1        | 1 | 0          | 1              | $d_2$          | d <sub>1</sub> | d <sub>0</sub>  | mg              | m <sub>7</sub> | $d_2$          | $d_1$          | d <b>0</b>     | 0               | 1              | p <sub>3</sub>   | p <sub>2</sub> |

| JRL      | Jump/test right PR bits | 1        | 1 | 1          | 1              | 1              | d <sub>1</sub> | $d_0$           | mg              | m <sub>7</sub> | 1              | d <sub>1</sub> | $d_{0}$        | 1               | 1              | p <sub>1</sub>   | p <sub>0</sub> |

| JPX      | Jump/test PX-bus        | 1        | 1 | 1          | 1              | 0              | d <sub>1</sub> | d <sub>0</sub>  | mg              | m <sub>7</sub> | m <sub>6</sub> | d <sub>1</sub> | d <b>o</b>     | ×7              | ×6             | ×5               | <b>×</b> 4     |

#### NOTE:

dn = Data pm address control line n

$m_n$  = Data in microprogram address register bit n

pn = Data in PR-latch bit n

$x_n$  = Data on PX-bus line n (active LOW)

f, c, z = Contents of F-latch, C-flag, or Z-flag, respectively

#### STROBE FUNCTIONS Cont'd.

the fetch/execute cycle. The interrupt control responds to the interrupt by pulling the enable row address (ERA) input line low to override the selected next row address from the MCU. Then by gating an alternative next row address on to the row address lines of the microprogram memory, the microprogram may be forced to enter an interrupt handling routine. The alternative row address placed on the microprogram memory address lines does not alter the contents of the microprogram address register. Therefore, subsequent jump functions will utilize the row address in the register, and not the alternative row address, to determine the next microprogram address.

Note, the load function always overrides the address control function on  $AC_0-AC_6$ . It does not, however, override the latch enable or load sub-functions of the JCE or JPX instruction, respectively. In addition, it does not inhibit the interrupt strobe enable or any of the flag control functions.

#### FLAG CONTROL FUNCTION SUMMARY

| TYPE  | MNEMONIC | DESCRIPTION                | FC <sub>1</sub> | 0 |

|-------|----------|----------------------------|-----------------|---|

|       | SCZ      | Set C-flag and Z-flag to f | 0               | 0 |

| Flag  | STZ      | Set Z-flag to f            | 0               | 1 |

| Input | STC      | Set C-flag to f            | 1               | 0 |

|       | HCZ      | Hold C-flag and Z-flag     | 1               | 1 |

| TYPE           | MNEMONIC | DESCRIPTION        | FC <sub>3</sub> | 2 |

|----------------|----------|--------------------|-----------------|---|

|                | FF0      | Force FO to 0      | 0               | 0 |

| Flag           | FFC      | Force FO to C-flag | 0               | 1 |

| Flag<br>Output | FFZ      | Force FO to Z-flag | 1               | 0 |

|                | FF1      | Force FO to 1      | 1               | 1 |

| LOAD<br>FUNCTION |                 | NEX            | EXT ROW |    |                | N      | EXT  | со    | L  |

|------------------|-----------------|----------------|---------|----|----------------|--------|------|-------|----|

| LD               | MA <sub>8</sub> | 7              | 6       | 5  | 4              | $MA_3$ | 2    | 1     | 0  |

| 0                | See A           | pper           | ndix    | Α  |                | See Ap | penc | lix A |    |

| 1                | 0               | x <sub>3</sub> | ×2      | ×1 | × <sub>0</sub> | ×7     | ×6   | ×5    | ×4 |

#### NOTE:

f = Contents of the F-latch

$x_n = Data on PX- or SX-bus line n (active LOW)$

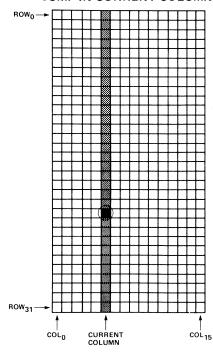

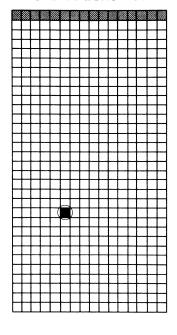

#### JUMP SET DIAGRAMS

The following ten diagrams illustrate the jump set for each of the eleven jump and jump/test functions of the MCU. Location 341 indicated by the circled square, represents one current row ( $row_{21}$ ) and current column ( $col_5$ )

address. The dark boxes indicate the microprogram locations that may be selected by the particular function as the next address.

JZR JUMP TO ZERO ROW

#### JUMP SET DIAGRAMS Cont'd.

#### JUMP SET DIAGRAMS Cont'd.

### AC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = 5.0V + 5\%$

|                  | DADAMETER                                                                                             |     | LIMITS           |     | LINIT |

|------------------|-------------------------------------------------------------------------------------------------------|-----|------------------|-----|-------|

|                  | PARAMETER                                                                                             | MIN | TYP <sup>1</sup> | MAX | UNIT  |

| t <sub>CY</sub>  | Cycle Time                                                                                            | 60  | 45               |     | ns    |

| t <sub>WP</sub>  | Clock Pulse Width                                                                                     | 17  | 10               |     | ns    |

|                  | Control and Data Input Set-Up Times:                                                                  |     |                  |     |       |

| t <sub>SF</sub>  | LD, $AC_0 - AC_6$                                                                                     | 7   | 0                |     | ns    |

| tsĸ              | FC <sub>0</sub> , FC <sub>1</sub>                                                                     | 7   | 0                |     | ns    |

| t <sub>SX</sub>  | $SX_0-SX_3$ , $PX_4-PX_7$                                                                             | 28  | 20               |     | ns    |

| tsı              | FI                                                                                                    | 12  | 0                |     | ns    |

|                  | Control and Data Input Hold Times:                                                                    |     |                  |     |       |

| tHF              | $LD, AC_0-AC_6$                                                                                       | 4   | 0                |     | ns    |

| tHK              | $FC_0$ , $FC_1$                                                                                       | 4   | 0                |     | ns    |

| t <sub>HX</sub>  | $SX_0-SX_3$ , $PX_4-PX_7$                                                                             | 16  | 0                |     | ns    |

| $t_{HI}$         | FI                                                                                                    | 16  | 6                |     | ns    |

| tco              | Propagation Delay from Clock Input (CLK) to Outputs $(MA_0-MA_8, FO)$                                 |     | 24               | 36  | ns    |

| t <sub>K</sub> O | Propagation Delay from Control Inputs $FC_2$ and $FC_3$ to Flag Out (FO)                              |     | 13               | 24  | ns    |

| t <sub>FO</sub>  | Propagation Delay from Control Inputs $AC_0 - AC_6$ to Latch Outputs ( $PR_0 - PR_2$ )                |     | 21               | 32  | ns    |

| t <sub>EO</sub>  | Propagation Delay from Enable Inputs EN and ERA to Outputs (MA $_0$ -MA $_8$ , FO, PR $_0$ -PR $_2$ ) |     | 17               | 26  | ns    |

| t <sub>Fl</sub>  | Propagation Delay from Control Inputs $AC_0-AC_6$ to Interrupt Strobe Enable Output (ISE)             |     | 19               | 32  | ns    |

#### NOTE:

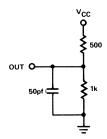

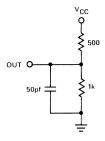

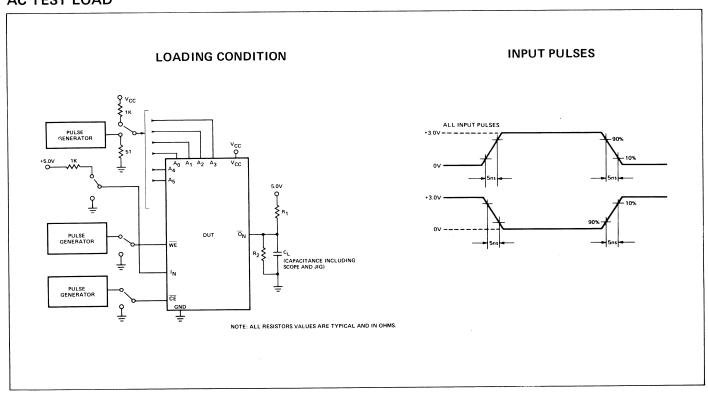

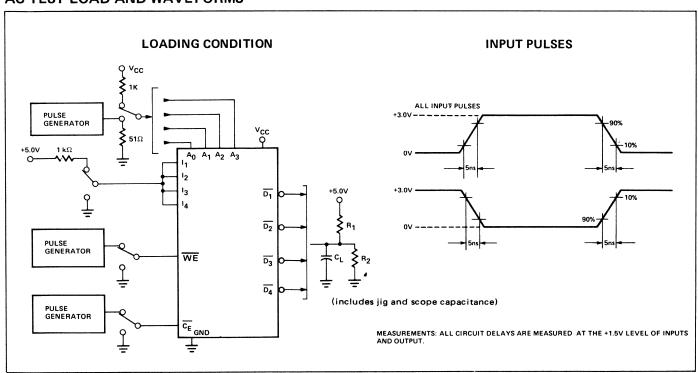

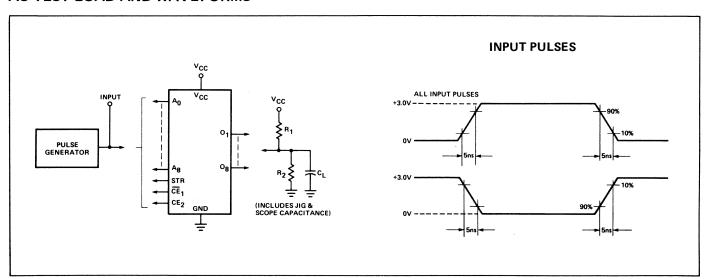

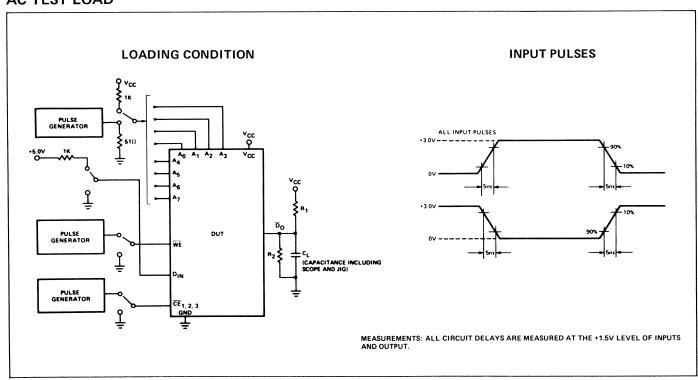

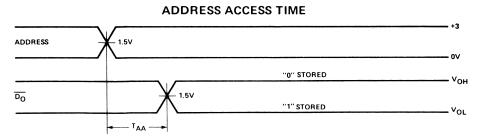

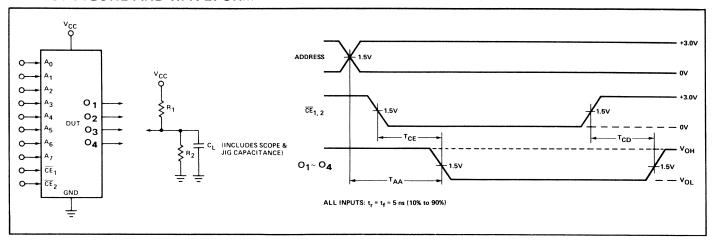

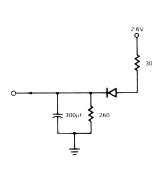

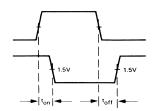

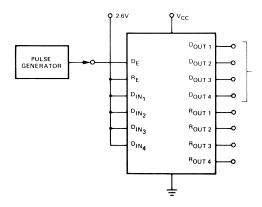

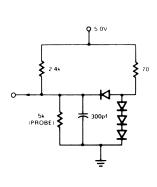

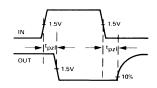

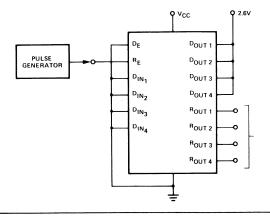

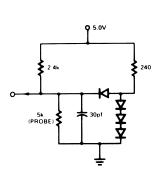

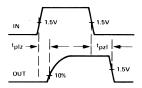

#### PARAMETER MEASUREMENT INFORMATION

#### **LOAD CIRCUIT**

NOTE: ALL RESISTORS VALUES ARE TYPICAL AND IN OHMS.

#### **TEST CONDITIONS**

Input pulse amplitude of 2.5 volts.

Input rise and fall times of 5ns between 1 volt and 2 volts.

Output load of 10mA and 50pF.

Speed measurements are taken at the 1.5 volt level.

<sup>1.</sup> Typical values are for  $T_A = 25^{\circ} C$  and 5.0 supply voltage.

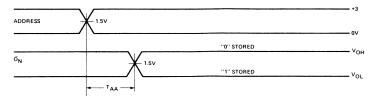

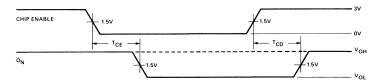

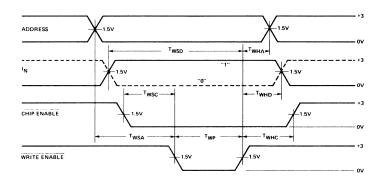

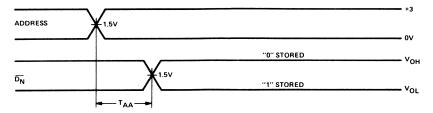

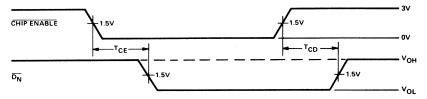

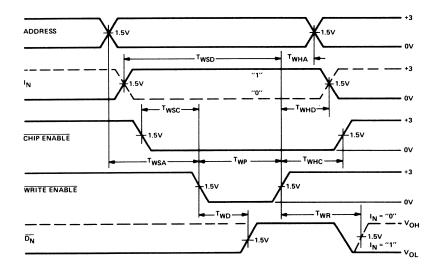

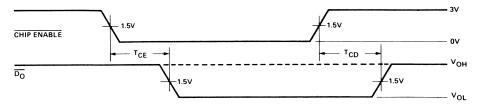

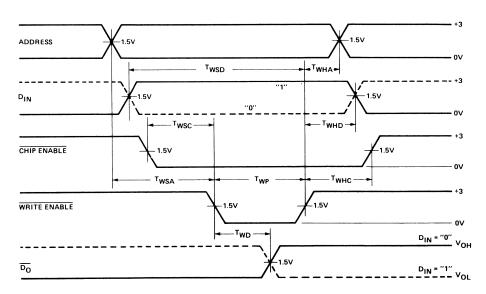

#### **VOLTAGE WAVEFORMS**

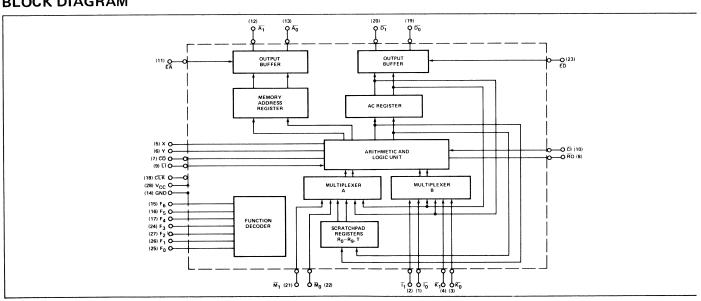

# CENTRAL PROCESSING ELEMENT | N3002

#### **PRELIMINARY**

#### **DESCRIPTION**

The N3002 Central Processing Element (CPE) is one part of a bipolar microcomputer set. The N3002 is organized as a 2-bit slice and performs the logical and arithmetic functions required by micro - instructions. A system with any number of bits in a data word can be implemented by using multiple N3002s, the N3001 microcomputer control unit, the N74S182 carry look-ahead unit and ROM or PROM memory.

#### **FEATURES**

- 45ns CYCLE TIME (TYP.)

- **EASY EXPANSION TO MULTIPLE OF 2 BITS**

- 11 GENERAL PURPOSE REGISTERS

- **FULL FUNCTION ACCUMULATOR**

- **USEFUL FUNCTIONS INCLUDE:** 2's COMPLEMENT ARITHMETIC LOGICAL AND, OR, NOT, EXCLUSIVE-NOR **INCREMENT, DECREMENT** SHIFT LEFT/SHIFT RIGHT **BIT TESTING AND ZERO DETECTION CARRY LOOK-AHEAD GENERATION MASKING VIA K-BUS** CONDITIONED CLOCKING ALLOWING NON-DESTRUCTIVE TESTING OF DATA IN ACCU-**MULATOR AND SCRATCHPAD**

- 3 INPUT BUSSES

- **2 OUTPUT BUSSES**

- CONTROL BUS

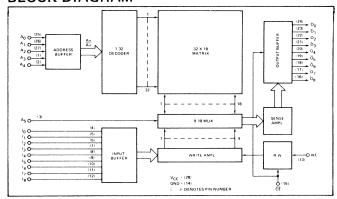

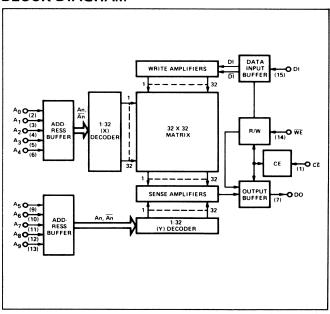

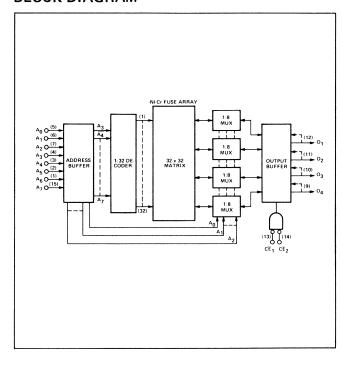

#### **BLOCK DIAGRAM**

## BIPOLAR MICROPROCESSOR

#### PIN CONFIGURATION

#### PIN DESCRIPTION

| PIN             | SYMBOL                         | NAME AND FUNCTION                                                                                                                                                                                  | TYPE                      |

|-----------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1, 2            | I <sub>0</sub> —I <sub>1</sub> | External Bus Inputs  The external bus inputs provide a separate input port for external input devices.                                                                                             | Active LOW                |

| 3, 4            | K <sub>0</sub> -K <sub>1</sub> | Mask Bus Inputs The mask bus inputs provide a separate input port for the microprogram memory, to allow mask or constant entry.                                                                    | Active LOW                |

| 5, 6            | X, Y                           | Standard Carry Look-Ahead Cascade Outputs The cascade outputs allow high speed arithmetic operations to be performed when they are used in conjunction with the 74S182 Look-Ahead Carry Generator. | Active HIGH               |

| 7               | со                             | Ripple Carry Output  The ripple carry output is only disabled during shift right operations.                                                                                                       | Active LOW<br>Three-state |

| 8               | RO                             | Shift Right Output The shift right output is only enabled during shift right operations.                                                                                                           | Active LOW<br>Three-state |

| 9               | LI                             | Shift Right Input                                                                                                                                                                                  | Active LOW                |

| 10              | CI                             | Carry Input                                                                                                                                                                                        | Active LOW                |

| 11              | EA                             | Memory Address Enable Input When in the LOW state, the memory address enable input enables the memory address outputs $(A_0-A_1)$ .                                                                | Active LOW                |

| 12–13           | $A_0-A_1$                      | Memory Address Bus Outputs The memory address bus outputs are the buffered outputs of the memory address register (MAR).                                                                           | Active LOW<br>Three-state |

| 14              | GND                            | Ground                                                                                                                                                                                             |                           |

| 15–17,<br>24–27 | F <sub>0</sub> -F <sub>6</sub> | Micro-Function Bus Inputs The micro-function bus inputs control ALU function and register selection.                                                                                               | Active-HIGH               |

| 18              | CLK                            | Clock Input                                                                                                                                                                                        |                           |

| 19–20           | D <sub>0</sub> -D <sub>1</sub> | Memory Data Bus Outputs  The memory data bus outputs are the buffered outputs of the full function accumulator register (AC).                                                                      | Active LOW<br>Three-state |

| 21–22           | $M_0-M_1$                      | Memory Data Bus Inputs The memory data bus inputs provide a separate input port for memory data.                                                                                                   | Active LOW                |

| 23              | ED                             | Memory Data Enable Input When in the LOW state, the memory data enable input enables the memory data outputs ( $D_0-D_1$ ).                                                                        | Active LOW                |

| 28              | $v_{cc}$                       | +5 Volt Supply                                                                                                                                                                                     |                           |

#### SYSTEM DESCRIPTION

#### 1. MICROFUNCTION DECODER AND K-BUS

Basic microfunctions are controlled by a 7-bit bus ( $F_0-F_6$ ) which is organized into two groups. The higher 3 bits ( $F_4-F_6$ ) are designated as F-Group and the lower 4 bits ( $F_0-F_3$ )

are designated as the R-Group. The F-Group specifies the type of operation to be performed and the R-Group specifies the registers involved.

#### **SYSTEM DESCRIPTION (Continued)**

The F-Bus instructs the microfunction decoder to:

- Select ALU functions to be performed

- Generate scratchpad register address

- Control A and B multiplexer

The resulting microfunction action can be:

- Data transfer

- Shift operations

- Increment and decrement

- Initialize stack

- Test for zero conditions

- 2's complement addition and subtraction

- Bit masking

- Maintain program counter

#### 2. A AND B MULTIPLEXERS

A and B multiplexers select the proper two operands to the ALU.

A multiplexer selects inputs from one of the following:

- M-bus (data from main memory)

- Scratchpad registers

- Accumulator

B multiplexer selects inputs from one of the following:

- I-bus (data from external I/O devices)

- Accumulator

- K-bus (literal or masking information from microprogram memory)

#### 3. SCRATCHPAD REGISTERS

- Contains 11 registers (R<sub>0</sub>-R<sub>9</sub>, T)

- Scratchpad register outputs are multiplexed to the ALU via the A multiplexer

- Used to store intermediate results from arithmetic/logic operations

- Can be used as program counter

#### 4. ARITHMETIC/LOGIC UNIT (ALU)

The ALU performs the arithmetic and logic operations of the CPE.

Arithmetic operations are:

- 2's complement addition

- Incrementing

- Decrementing

- Shift left

- Shift right

Logical operations are:

- Transfer

- AND

- Inclusive-OR

- Exclusive-OR

- Logic complement

ALU operation results are then stored in the accumulato and/or scratchpad registers. For easy expansion to large arrays, carry look-ahead outputs (X and Y) and cascading shift inputs (LI, Ro) are provided.

#### 5. ACCUMULATOR

- Stores results from ALU operations

- The output of accumulator is multiplexed into ALU vir the A and B multiplexer as one of the operands

#### 6. INPUT BUSES

M-bus Data bus from main memory

- Accepts 2 bits of data from main memory into CPE

- Is multiplexed into the ALU via the A multiplexer

I-bus Data bus from input/output devices

- Accepts 2 bits of data from external input/outpur devices into CPE

- Is multiplexed into the ALU via the B multiplexer

K-bus A special feature of the N3002 CPE

- During arithmetic operations, the K-bus can be used to mask portions of the field being operated on

- Select or remove accumulator from operation by placing K-bus in all "1" or all "0" state respectively

- During non-arithmetic operation, the carry circuit can be used in conjunction with the K-bus for word-wise-OR operation for bit testing

- Supply literal or constant data to CPE

#### 7. OUTPUT BUSES

A-bus and Memory Address Register

- Main memory address is stored in the memory address register (MAR)

- Main memory is addressed via the A-bus

- MAR and A-bus may also be used to generate device address when executing I/O instructions

- A-bus has Tri-State outputs

D-bus Data bus from CPE to main memory or to I/O

- Sends buffered accumulator outputs to main memory or the external I/O devices

- D-bus has Tri-State outputs

#### **FUNCTION DESCRIPTION**

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                                                                                                                                                                                                         | DESCRIPTION                                                                                                                                                                                       |

|------------|------------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | 1          | xx       |      | $R_n + (AC \wedge K) + CI \rightarrow R_n, AC$                                                                                                                                                                   | Logically AND AC with the K-bus. Add the result to ${\sf R}_{\sf n}$ and carry input (CI). Deposit the sum in AC and ${\sf R}_{\sf n}$ .                                                          |

|            |            | 00       | ILR  | $R_n + CI \rightarrow R_n$ , AC                                                                                                                                                                                  | Conditionally increment $R_n$ and load the result in AC. Used to load AC from $R_n$ or to increment $R_n$ and load a copy of the result in AC.                                                    |

|            |            | П        | ALR  | $AC + R_n + CI \rightarrow R_n$ , $AC$                                                                                                                                                                           | Add AC and CI to $\mathbf{R}_n$ and load the result in AC. Used to add AC to a register. If $\mathbf{R}_n$ is AC, then AC is shifted left one bit position.                                       |

| 0          | П          | xx       |      | $M + (AC \wedge K) + CI \rightarrow AT$                                                                                                                                                                          | Logically AND AC with the K-bus. Add the result to CI and the M-bus. Deposit the sum in AC or T.                                                                                                  |

|            |            | 00       | ACM  | $M + CI \rightarrow AT$                                                                                                                                                                                          | Add CI to M-bus. Load the result in AC or T, as specified. Used to load memory data in the specified register, or to load incremented memory data in the specified register.                      |

|            |            | 11       | AMA  | $M + AC + CI \rightarrow AT$                                                                                                                                                                                     | Add the M-bus to AC and CI, and load the result in AC or T, as specified. Used to add memory data or incremented memory data to AC and store the sum in the specified register.                   |

| 0          | Ш          | xx       | -    | $\begin{array}{c} AT_L \wedge (\overline{I_L \wedge K_L}) \to RO \\ LI \vee \{(II_H \wedge K_H) \wedge AT_H\} \to AT_H \\ [AT_L \wedge (I_L \wedge K_L)] \vee [AT_H \vee (I_H \wedge K_H)] \to AT_L \end{array}$ | None                                                                                                                                                                                              |

|            |            | 00       | SRA  | AT <sub>L</sub> → RO AT <sub>H</sub> → AT <sub>L</sub> LI → AT <sub>H</sub>                                                                                                                                      | Shift AC or T, as specified, right one bit position. Place the previous low order bit value on RO and fill the high order bit from the data on LI. Used to shift or rotate AC or T right one bit. |

| 1          | ı          | ××       | _    | $K \lor R_n \to MAR$<br>$R_n + K + CI \to R_n$                                                                                                                                                                   | Logically OR $R_n$ with the K-bus. Deposit the result in MAR. Add the K-bus to $R_n$ and CI. Deposit the result in $R_n$ .                                                                        |

|            |            | 00       | LMI  | $R_n \rightarrow MAR$ $R_n + CI \rightarrow R_n$                                                                                                                                                                 | Load MAR from $R_{\mbox{\scriptsize n}}.$ Conditionally increment $R_{\mbox{\scriptsize n}}.$ Used to maintain a macro-instruction program counter.                                               |

|            |            | Ħ        | DSM  | $11 \rightarrow MAR$ $R_n - 1 + CI \rightarrow R_n$                                                                                                                                                              | Set MAR to all one's. Conditionally decrement $\mathbf{R}_{n}$ by one. Used to force MAR to its highest address and to decrement $\mathbf{R}_{n}$ .                                               |

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                                                    |                                                                                                                                                                                                                 |  |  |

|------------|------------|----------|------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | П          | ××       | _    | K V M → MAR<br>M + K + CI → AT                              | Logically OR the M-bus with the K-bus. Deposit the result in MAR. Ad the K-bus to the M-bus and CI. Deposit the sum in AC or T.                                                                                 |  |  |

|            |            | 00       | LMM  | $M \rightarrow MAR$ $M + CI \rightarrow AT$                 | Load MAR from the M-bus. Add CI to the M-bus. Deposit the result in AC or T. Used to load the address register with memory data for macroinstructions using indirect addressing.                                |  |  |

|            |            | 11       | LDM  | 11 → MAR<br>M - 1 + CI → AT                                 | Set MAR to all ones. Subtract one from the M-bus. Add CI to the difference and deposit the result in AC or T, as specified. Used to load decremented memory data in AC or T.                                    |  |  |

| 1          | 111        | ××       | _    | $\overline{(AT} \lor K) + (AT \land K) + CI \rightarrow AT$ | Logically OR the K-bus with the complement of AC or T, as specified.  Add the result to the logical AND of specified register with the K-bus.  Add the sum to CI. Deposit the result in the specified register. |  |  |

|            |            | 00       | CIA  | AT + CI → AT                                                | Add CI to the complement of AC or T, as specified. Deposit the result in the specified register. Used to form the 1's or 2's complement of AC or T.                                                             |  |  |

|            |            | 11       | DCA  | AT - 1 + CI → AT                                            | Subtract one from AC or T, as specified. Add CI to the difference and deposit the sum in the specified register. Used to decrement AC or T.                                                                     |  |  |

| 2          | 1 .        | XX       | _    | (AC Λ K) – 1 + Cl → R <sub>n</sub><br>(See Note 1)          | Logically AND the K-bus with AC. Subtract one from the result and add the difference to CI. Deposit the sum in $\rm R_{\rm n}$ .                                                                                |  |  |

|            |            | 00       | CSR  | CI − 1 → R <sub>n</sub><br>(See Note 1)                     | Subtract one from CI and deposit the difference in ${\bf R}_n.$ Used to conditionally clear or set ${\bf R}_n$ to all 0's or 1's, respectively.                                                                 |  |  |

|            |            | П        | SDR  | AC - 1 + Cl → R <sub>n</sub><br>(See Note 1)                | Subtract one from AC and add the difference to CI. Deposit the sum in ${\bf R}_n.$ Used to store AC in ${\bf R}_n$ or to store the decremented value of AC in ${\bf R}_n.$                                      |  |  |

| 2          | 11         | xx       | _    | (AC ∧ K) - 1 + CI → AT                                      | Logically AND the K-bus with AC. Subtract one from the result and add the difference to CI. Deposit the sum in AC or T, as specified.                                                                           |  |  |

|            |            | 00       | CSA  | (See Note 1)<br>CI − 1 → AT<br>(See Note 1)                 | Subtract one from CI and deposit the difference in AC or T. Used to conditionally clear or set AC or T.                                                                                                         |  |  |

|            |            | H        | SDA  | AC - 1 + CI → AT<br>(See Note 1)                            | Subtract one from AC and add the difference to CI. Deposit the sum in AC or T. Used to store AC in T, or decrement AC, or store the decremented value of AC in T.                                               |  |  |

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                              | DESCRIPTION                                                                                                                                                                                          |

|------------|------------|----------|------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2          | 111        | xx       | _    | (I ∧ K) – 1 + CI → AT<br>(See Note 1) | Logically AND the data of the K-bus with the data on the I-bus. Subtract one from the result and add the difference to CI. Deposit the sum in AC or T, as specified.                                 |

|            |            | 00       | CAS  | CI -1 →AT                             | Subtract one from CI and deposit the difference in AC or T. Used to conditionally clear or set AC or T.                                                                                              |

|            |            | 11       | LDI  | I – 1 + CI → AT                       | Subtract one from the data on the I-bus and add the difference to CI. Deposit the sum in AC or T, as specified. Used to load input bus data or decremented input bus data in the specified register. |

| 3          | ı          | xx       | _    | $R_n + (AC \wedge K) + CI \to R_n$    | Logically AND AC with the K-bus. Add $R_n$ and CI to the result. Deposit the sum in $R_n.$                                                                                                           |

|            |            | 00       | INR  | $R_n + CI \rightarrow R_n$            | Add CI to $R_n$ and deposit the sum in $R_n$ . Used to increment $R_n$ .                                                                                                                             |

|            |            | 11       | ADR  | $AC + R_n + CI \rightarrow R_n$       | Add AC to $R_{\rm n}$ . Add the result to CI and deposit the sum in $R_{\rm n}$ . Used to add the accumulator to a register or to add the incremented value of the accumulator to a register.        |

| 3          | П          | xx       | _    | $M + (AC \land K) + CI \to AT$        | <b>Logically AND AC with the K-bus.</b> Add the result to CI and the M-bus Deposit the sum in AC or T.                                                                                               |

|            |            | 00       | ACM  | M + CI → AT                           | Add CI to M-bus. Load the result in AC or T, as specified. Used to load memory data in the specified register, or to load incremented memory data in the specified register.                         |

|            |            | 11       | AMA  | M + AC + CI → AT                      | Add the M-bus to AC and CI, and load the result in AC or T, as specified. Used to add memory data or incremented memory data to AC and store the sum in the specified register.                      |

| 3          | Ш          | ××       | _    | AT + (I ∧ K) + CI → AT                | Logically AND the K-bus with the I-bus. Add CI and the contents of AC or T, as specified, to the result. Deposit the sum in the specified register.                                                  |

|            |            | 00       | INA  | $AT + CI \rightarrow AT$              | Conditionally increment AC or T. Used to increment AC or T.                                                                                                                                          |

|            |            | П        | AIA  | I + AT + CI → AT                      | Add the I-bus to AC or T. Add CI to the result and deposit the sum in the specified register. Used to add input data or incremented input data to the specified register.                            |

#### **FUNCTION TRUTH TABLE**

| FUNCTION<br>GROUP |  |                |   |   | 5              |                | F <sub>4</sub> |   |

|-------------------|--|----------------|---|---|----------------|----------------|----------------|---|

| 0                 |  | 0              |   | 0 |                |                | 0              |   |

| 1                 |  | 0              |   |   | 0              |                | 1              |   |

| 2                 |  | 0              |   |   | 1              |                | 0              |   |

| 2 3               |  | 0              |   |   | 1              |                | 1              |   |

| 4                 |  | 1              |   |   | 0              |                | 0              |   |

| 5                 |  | 1              |   |   | 0              |                | 1              |   |

| 6                 |  | 1              |   |   | 1              |                | 0              |   |

| 7                 |  | 1              |   |   | 1              |                | 1              |   |

| REGISTER<br>GROUP |  |                |   | 3 | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub> |   |

|                   |  | R <sub>0</sub> |   | 0 | 0              | 0              | 0              |   |

|                   |  | R <sub>1</sub> |   | 0 | 0              | 0              | 1              |   |

|                   |  | R <sub>2</sub> |   | 0 | 0              | 1              | 0              |   |

|                   |  | R <sub>3</sub> | 1 | 0 | 0              | 1              | 1              |   |

|                   |  | R <sub>4</sub> |   | 0 | 1              | 0              | 0              |   |

|                   |  | R <sub>5</sub> |   | 0 | 1              | 0              | 1              |   |

| '                 |  | R <sub>6</sub> |   | 0 | 1              | 1              | 0              |   |

|                   |  | R <sub>7</sub> |   | 0 | 1              | 1              | 1              |   |

|                   |  | R <sub>8</sub> |   | 1 | 0              | 0              | 0              |   |

|                   |  | Rg             |   | 1 | 0              | 0              | 1              |   |

|                   |  | T              |   | 1 | 1              | 0              | 0              |   |

|                   |  | AC             |   | 1 | 1              | 0              | 1              |   |

| 11                |  | T              |   | 1 | 0              | 1              | 0              | ł |

| 11                |  | AC             |   | 1 | 0              | 1              | 11             |   |

| 111               |  | Т              |   | 1 | 1              | 1              | 0              |   |

|                   |  | AC             |   | 1 | 1              | 1              | 1              |   |

| SYMBOL         | MEANING                                                       |

|----------------|---------------------------------------------------------------|

| I, K, M        | Data on the I, K, and M busses, respectively                  |

| CI, LI         | Data on the carry input and left input, respectively          |

| CO, RO         | Data on the carry output and right output, respectively       |

| R <sub>n</sub> | Contents of register n including T and AC (R-Group I)         |

| AC             | Contents of the accumulator                                   |

| AT             | Contents of AC or T, as specified                             |

| MAR            | Contents of the memory address register                       |

| L, H           | As subscripts, designate low and high order bit, respectively |

| +              | 2's complement addition                                       |

| Arre-          | 2's complement subtraction                                    |

| ^              | Logical AND                                                   |

| \ \ \          | Logical OR                                                    |

| <u>⊕</u>       | Exclusive-NOR                                                 |

| <b>→</b>       | Deposit into                                                  |

NOTE:

1. 2's complement arithmetic adds 111 . . . 11 to perform subtraction of 000 . . . 01.

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                                                                                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                               |

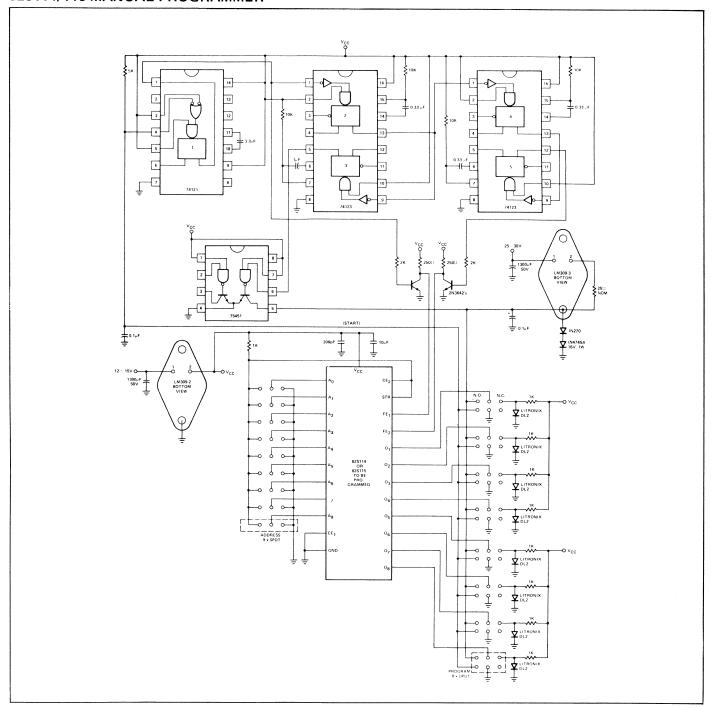

|------------|------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|